在2月16日举行的国际固态电路会议ISSCC上,合乐HL8注册登录徐鸿涛教授带领的WiCAS(无线集成电路与系统)课题组在高性能CMOS数字功率放大器的设计方面再次发表研究突破。该课题组在高性能CMOS功率放大器设计研究上提出了多项原创性技术,使高效率高功率的数字功率放大器更容易应用在宽带无线通信上,相关成果已连续三年在国际固态电路会议上亮相(ISSCC 2018/2019/2020)。ISSCC是集成电路设计领域的国际顶级会议,是国际学术界和顶尖半导体公司的研发人员发布先进成果和最新进展的重要窗口,在国际半导体技术界具有重要的影响力。

功率放大器是无线系统的核心模块,直接影响着整个系统的性能、功耗和成本。射频前端芯片逐步与数字基带芯片实现全集成,持续提升4G/5G/WiFi等无线技术的用户体验。但是随着CMOS工艺向纳米尺寸缩小,高衬底损耗、低电源电压、低击穿电压等问题的不断显现,使得高性能的CMOS功率放大器集成成为业界的研究难点,从而影响到了整个通信系统的电池寿命和封装热处理等方面。

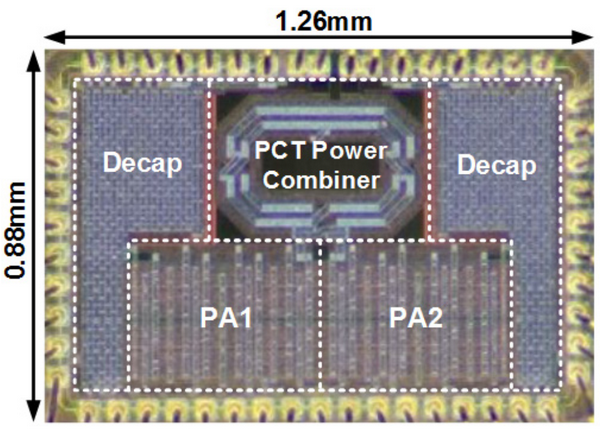

2018年,WiCAS课题组提出一种新型的数字式射频功率合成技术,仅用约1平方毫米的芯片面积实现NBIOT双频带功率合成(如下图)。另外,借助数字化控制实现Doherty负载调制以提升回退效率,在效率曲线上实现了2个峰值(0/6dB),相比于传统功率放大器显著提高了平均发射效率。该研究成果成功发表在ISSCC 2018会议上,该芯片以紧凑的芯片面积实现了近瓦级的输出功率、双频带覆盖以及较高的平均发射效率,特别适用于低成本的物联网等无线通信应用场景。

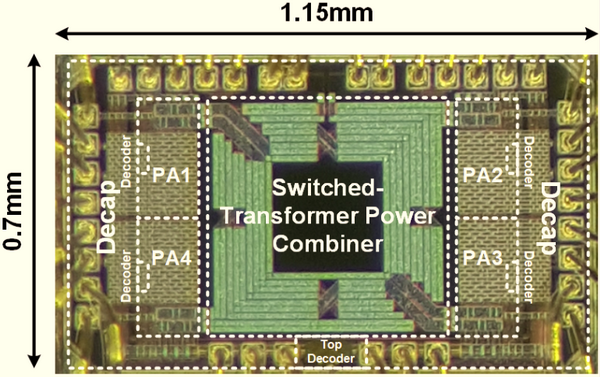

2019年,WiCAS课题组针对LTE、WLAN等宽带应用的高峰均比和大动态范围需求,进一步提出18dB深回退效率增强方案,采用了新型的开关变压器技术,首次在效率曲线上实现了4个峰值(0/6/12/18dB),在不增加芯片成本的情况下,实现整体性能的提升。该研究成果成功发表在ISSCC 2019会议上,在40nm CMOS工艺上,用1.1V单电源供电,芯片面积仅0.8平方毫米(如下图)。该成果为未来5G通信进一步提高集成度和能效提供了有力的技术支撑。

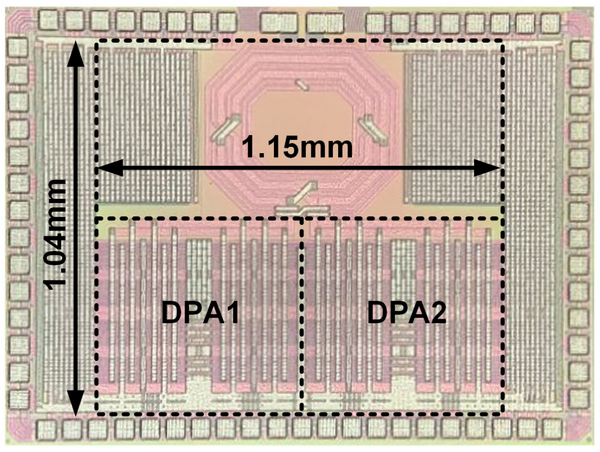

2020年,课题组针对更适合宽带无线通信系统的笛卡尔架构,提出了一种基于变压器合成的复数域负载调制方案,使笛卡尔功率放大器的输出功率和效率达到了与极坐标架构相比拟的水平。在今年ISSCC 2020会议上发表的芯片,实现接近1瓦的峰值功率,峰值效率43.1%。在发射LTE信号时,芯片效率达24.4%,而且在不增加芯片成本和复杂度的前提下,该芯片实现了15bit高精度和大动态范围,适用于5G、WLAN等宽带通信系统。

未来,该研究团队将进一步开展超宽带、高效率、高线性度功率放大器的研究应用,继续与学术界和产业界伙伴合作,努力实现数字式功率放大器的产业化、实用化,方便未来快速低成本地集成到单片全集成收发机中,有助于推动未来5G通信的快速发展。