在数字集成电路设计特别是基于FPGA的电路设计领域,越来越多的设计工程师开始使用高层次综合(High-levelSynthesis工具进行设计。高层次综合技术将电路设计抽象层次从当前的寄存器传输级(RegisterTransferLevel)提升到了C/C++、SystemC等更高的抽象层。电路设计者只需要利用C/C++或SystemC对电路进行描述,高层次综合工具自动将这些描述文件转换成高效的寄存器传输级描述文件。因此电路设计者可以从复杂繁琐的寄存器传输级设计中解脱出来,将更多的精力放在系统整体性能的优化上,从而大大提高了设计效率。

然而目前高层次综合工具所生成的寄存器传输级电路描述的质量与电路设计专家手工设计的电路描述相比仍然存在着较大的差距。其中的主要原因之一在于目前的高层次综合工具往往无法根据电路的C/C++、SystemC描述文件,综合出高效的存储器子系统。存储器存取性能和处理器运算性能之间的差距越来越大,使得在一个电路系统中,存储器子系统往往成为整个系统的性能瓶颈。因此综合出高效的存储子系统对高层次综合工具至关重要。

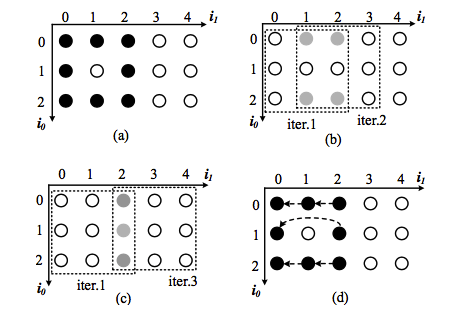

针对存储器并行访问需求和存储器带宽有限之间的矛盾,实验室曾璇教授课题组提出了一个基于数据复用的存储器划分算法。该算法首先利用循环变换技术对源代码进行等价变换,提高代码数据复用性,然后利用一个数据复用策略将可复用的数据缓存在被组织成为寄存器链的片上寄存器中。该算法利用一个存储器划分策略将原存储阵列划分到多个不同的存储器块中,并将不能复用数据的存储器访问分别映射到这些存储器块上,从而使得这些存储器访问可以同时访问数据。与现有的存储器划分算法相比,对于大部分在图像视频处理和科学计算领域的应用来说,实验室所提出的划分算法在算法复杂度、硬件资源和功耗开销方面都具有很大的优势。

实验结果表明,所提出的算法执行时间少于一毫秒,可以将需要的存储块数目平均减少了59.7%,查找表数量平均减少了78.2%,触发器数量平均减少了65.5%,DSP48E数量则平均减少了59.7%,同时将整个存储器系统的动态功耗平均降低了74.8%。论文2017年被IEEETransactionsonComputer-AidedDesignofIntegratedCircuitsandSystems接收。

(a)PREWITT 图像滤波核的访存模式 (b)相邻迭代间的数据复用

(c)第一个迭代和第三个迭代之间的数据复用 (d)数据复用链