模拟电路相比数字电路对工艺参数偏差更敏感,在模拟电路设计中也通过匹配设计、差分设计等方法来降低工艺偏差的影响。随着工艺尺寸的缩小,即使采用了抗工艺偏差的设计,工艺随机偏差对电路性能影响也非常显著。复杂纳米工艺如亚波长光刻、化学机械抛光等导致制造的电路性能与设计标称值之间存在明显的偏差,对模拟电路成品率产生显著影响。

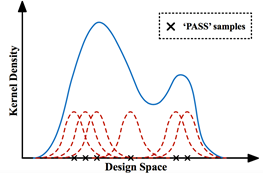

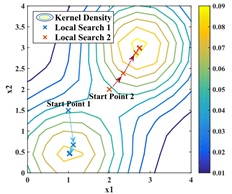

在面向成品率的模拟电路优化方面,实验室曾璇教授课题组通过贝叶斯公式将成品率优化问题转化为寻找设计点使得电路在工艺偏差下,在该设计点合格的概率密度最大的问题。对于该概率密度,可以通过已有的蒙特卡洛采样点,通过高斯核密度函数来进行逼近。工艺偏差下合格概率密度最大的问题就转化为高斯核密度函数最大化的问题。对于该问题,实验室提出一种类似期望-最大化(Expectation-Maximization,EM)的方法来进行快速求解。这种方法不需要不断的重复成品率估计,可以有效利用以前的仿真点来指导后续的优化;同时,期望-最大化方法具有解析公式,且收敛速度块。因此该方法相比传统的基于蒙特卡洛采样等方法进行成品率估计的优化方法,具有更高的优化效率。实验结果表明,相比现有的序列优化方法ORDE,可以将仿真点数目降低到原来的1/7以上,并且可以实现更高的成品率。该论文发表在电子设计自动化领域的最具影响力的国际会议IEEE/ACMDesignAutomationConference(DAC)2017,并获最佳论文提名。